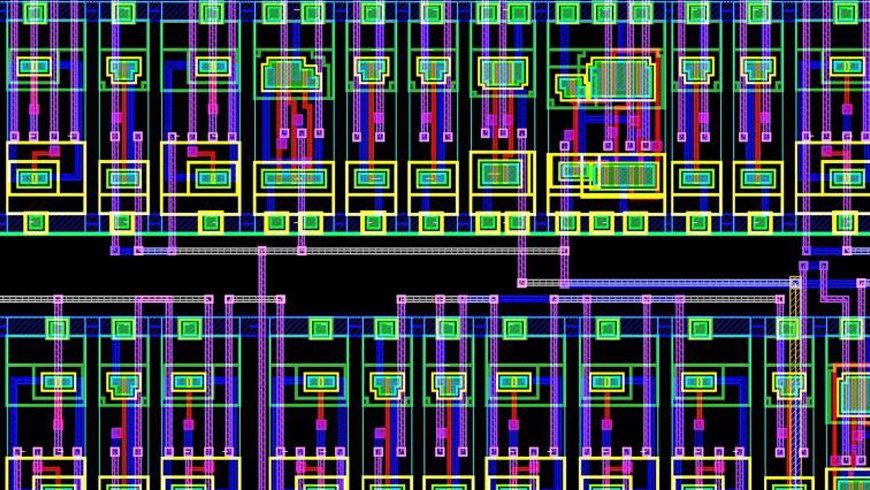

Vlsi

• Arithmetic building blocks form the back-bone of data path designs, and play a significant role in power consumption

• Standard-cell libraries were introduced few decades ago to help IC designers to address the challenge of the increasing complexity of IC design

• Main concern was to reduce the design cycle time & also cost of manufacturing

• But the convenience offered by predefined digital CMOS standard cells has come at the price of overall chip-level inefficiency

• One fit for all context is no longer true

STANDARD CELL DIRECTLY IMPACTS SYSTEM OPTIMIZATION

STATE OF THE ART SOLUTIONS

• Current Solutions are addressing the low power standard cell challenge by:

– Reducing Frequency

– Exploring different drive strength cells

– Most of the solutions are Physical parameter based such as Voltage:

• By reducing supply (Vdd) & cut-in voltages (Vt)

• By using different Materials with different di-electric

– Swapping low-Vt cells with high-Vt cells

To reduce leakage power (after timing closure)

• Modern day Semiconductor Industry challenges:

– Power, Reliability, Variability Manufacturability etc

• One of the primary drawback:

– Standard-cells are developed without knowing the context & are over-constrained

• The standard-cells are developed to achieve minimum foot print & fastest performance

• There exists ample opportunities to optimize power:

– If we relax the constraints

Customize as per particular Context

STATE OF THE ART SOLUTIONS LIMITATIONS

• Increased Design Cycle Time

– Design overhead

– Verification overhead

• Area Penalty

Risk of First Pass Silicon Success

Address

BHIVE MG Road, Mahalakshmi Chambers, 29, MG Road Next to Trinity Metro Station, opp. Kotak Bank, Bengaluru, Karnataka 560001

Phone

+91 98457 16571

cumapathy@banashreesystems.com